The PPU-200 series High Performance Parallel Processor (HP3) is a highly capable COTS based Parallel Processing Unit (PPU) that can achieve up to 200 MIPS on a single processing unit. Designed to provide high flexibility to enable use of COTS processor chips, HP3 provides high reliability and is scalable for intensive and extreme processing tasks, such as on-board imagery and payload processing, data mining, and precision navigation space applications.

The PPU-200 HP3 is designed to offer high speed processing and increased processing power to address the highly demanding space mission computing requirements for maximum mission efficiency and operation robustness. The highly adaptable application is able to support a variety of COTS software platforms, such as Linux, QNX OS, and OpenMP. Its proprietary on-chip communication design enables a fault tolerant and high bandwidth backbone to support parallel processing.

## **Key Features**

- Light weight high performance processing solution for intensive on-board processing applications

- Use of cost effective COTS components with no ITAR restrictions

- Supports up to 200 MIPS on a single processing board

- Equipped with autonomous fault management and offers high reliability performance with nominal performance probability at 99.51%

- Proven design with heritage from X-SAT

PPU-200 High Performance Parallel Processor (HP3)

## PPU-200 High Performance Parallel Processor (HP3)

## **Technical Specifications**

| Processing Power      | Up to 20 COTS processors in parallel<br>Up to 200 MIPS (depending on processor used)<br>Supports StrongArm, PowerPC, 8051, LEON |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| FPGA                  | Programmable ProAsic3 FPGA or<br>One-time-programmable RTAX Accelerator FPGA                                                    |

| Memory                | Fault Tolerant Serial Flash for boot code and application code  64 MB SDRAM / Processor                                         |

| Operating System      | Linux, QNX, VxWorks, RTEMS Supports OpenMP                                                                                      |

| Data Interface        | LVDS based Payload Input / Output (I/O) Interface<br>Option to support SpaceWire                                                |

|                       | Supports code upload, raw data reception and processed data transmission                                                        |

| CAN Network Interface | Telecommand and telemetry interface for configuration and code upload                                                           |

|                       | CAN network interface for short packet transmission, 500 kbps                                                                   |

| Dimension             | 300 mm x 250 mm x 35 mm (per module)                                                                                            |

| Mass                  | 800 g per module                                                                                                                |

| Power Consumption     | 10 W (peak memory operations)<br>5 W (standby memory operations)<br>28 V regulated supply                                       |

The PPU Payload - Adding value to missions by enabling computation-intensive image processing algorithms that maximises useful image data throughput from the satellite.

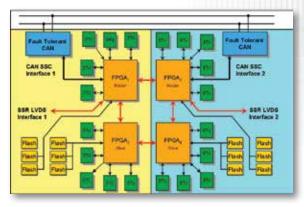

PPU Hardware Architecture

Note: All specifications are subject to change without notice. Rev. 140514